|

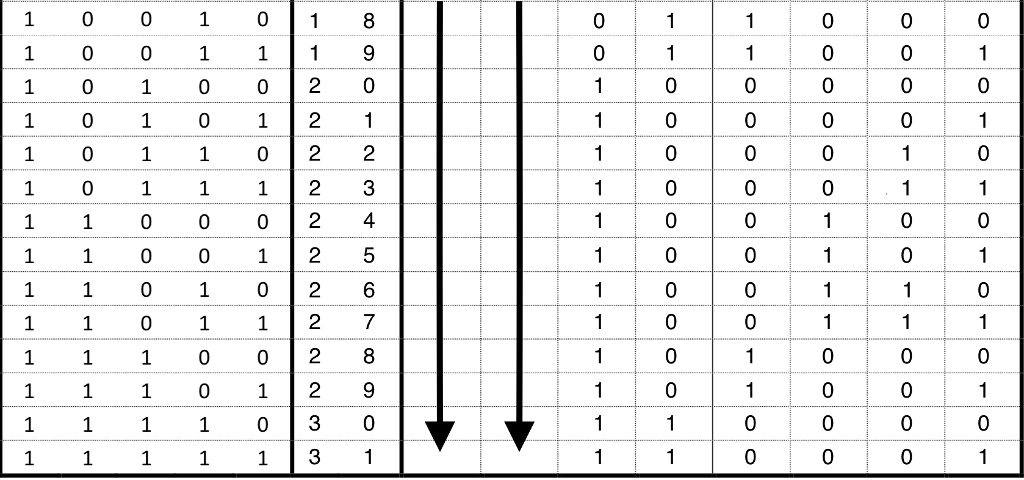

Exponent too small, floating point underflow, set to zero.Įnd else begin // // Case 2b: Adjust significand and exponent.Įnd end else begin // // Case 3: Sum is zero. if ( aneg ) asig = -asig īegin // / Step 6: Take absolute value of sum. If it were would need to set bexp = aexp īegin // / Step 4: If necessary, negate significands. Compute amount to shift significand and reduce exponent. I take a 3bit input, and need to output a 8bit. compile errors everywhere, Really frustrating. I think I keep getting confused with all the verilog, verilog-ams, verilog-A syntax. NOT verilog For a beginner like me, this is quite tough.

Find position of first non-zero digit.įor (i = 52 i >= 0 i = i - 1 ) if ( !pos & sumsig ) pos = i I am writing a verilog-A model for binary-to-thermometer decoder.

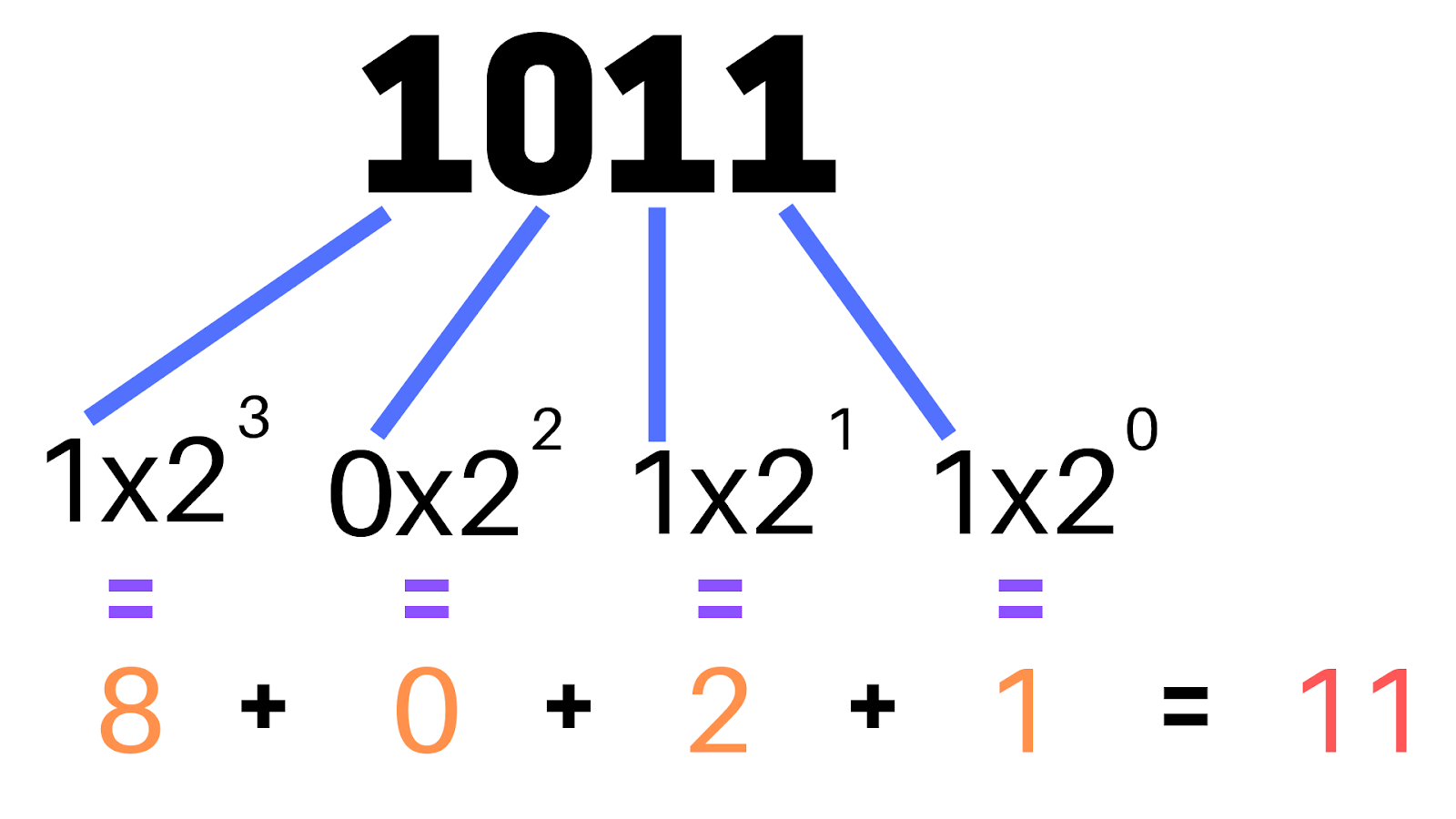

Right shift significand and increment exponent.Įnd else if ( sumsig ) begin: A // // Case 2: Sum is nonzero and did not overflow. (Three cases.) // if ( sumsig ) begin // // Case 1: Sum overflow. / Step 4: If necessary, negate significands. If it were would need to set bexp = aexp 31: S: Sign bit: 1 negative, 0 positive. / IEEE 754 Single Format // // Format: SEEEEEEEEFFFFFFFFFFFFFFFFFFFFFFF Significand may not include MSB (if not, it's 1). // Slight Complications (but for good reason): Can use signed integer magnitude and equality tests. + and - Infinity, and other special values. // Keep things simple for an introductory computer class. / Objectives of Standard // // Represent range of numbers in common use. NOTE: the final Verilog script in this video is intended for 4 digit conversion where the initial example is for 3 digit conversion.In this video we go t. Results of arithmetic operations, including rounding. / Standard Specifies // // Formats of FP numbers. / Multiplication Using Scientific Notation // // Consider: That is, right-shift b_scand by (a_exp - b_exp) bits. // Set b'scand = b_scand / 2^(a_exp - b_exp) // To convert decimal number x, 0 = 1/2, digit is 1, x = x - 1/2 // // Fixed Point Decimal to Binary Conversion

/ Binary Fixed Point Representation // // // Each digit position has a multiplier. Refer to the IEEE Std (1800-2009, for example), section 'Numbers'. For hexadecimal literals, you need to specify the literal type using h: keyschedule i1 h0A) // works keyschedule i1 h1D) // works. // Computer representations for FP numbers covered in the next section, Verilog treats all bare numeric literals as decimal. // Among other things, that means the number of bits needed to store a IEEE 754) are NOT computer representations. / Binary Floating-Point (FP) Representations // // The floating-point (FP) representations in this section (before / Binary Floating-Point Representation and Arithmetic // :PH: 3.5 / References // // :PH: Patterson & Hennessy, "Computer Organization & Design", 4th Edition L08.v // / LSU EE 3755 - Fall 2012 - Computer Organization // // / Verilog Notes 8 - Floating Point // Time-stamp: // / Contents // // Binary Floating-Point Representation and Arithmetic

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed